Musisz być zalogowany/a

-

WróćX

-

Alkatrészek

-

-

Kategória

-

Félvezetők

- Diódák

- Tirisztorok

-

Elektromosan szigetelt modulok

- VISHAY (IR) elektromosan szigetelt modulok

- INFINEON (EUPEC) elektro-szigetelt modulok

- A Semikron elektromosan szigetelt moduljai

- POWEREX elektroszigetelt modulok

- IXYS elektromosan szigetelt modulok

- Elektro-szigetelt modulok a POSEICO-tól

- Az ABB elektromosan szigetelt moduljai

- Elektro-szigetelt modulok a TECHSEM-től

- Przejdź do podkategorii

- Híd egyenirányítók

-

Tranzisztorok

- GeneSiC tranzisztorok

- Mitsubishi SiC MOSFET modulok

- STARPOWER SiC MOSFET modulok

- ABB SiC MOSFET modulok

- IGBT modulok a MITSUBISHI-tól

- MITSUBISHI tranzisztor modulok

- MITSUBISHI MOSFET modulok

- ABB tranzisztor modulok

- IGBT modulok a POWEREX-től

- IGBT modulok – az INFINEON-tól (EUPEC)

- Szilícium-karbid félvezető elemek

- Przejdź do podkategorii

- Drivers

- Tápblokkok

- Przejdź do podkategorii

- LEM áram- és feszültségátalakítók

-

Passzív alkatrészek (kondenzátorok, ellenállások, biztosítékok, szűrők)

- Ellenállások

-

Biztosítékok

- Miniatűr biztosítékok ABC és AGC sorozatú elektronikus rendszerekhez

- Gyors működésű cső alakú biztosítékok

- Késleltetett lapkák GL/GG és AM karakterisztikával

- Ultragyors biztosítékok

- Brit és amerikai szabványos gyors működésű biztosítékok

- Gyors működésű európai szabványú biztosítékok

- Vontatási biztosítékok

- Nagyfeszültségű biztosítékok

- Przejdź do podkategorii

-

Kondenzátorok

- Kondenzátorok motorokhoz

- Elektrolit kondenzátorok

- Jégfilm kondenzátorok

- Teljesítménykondenzátorok

- Kondenzátorok egyenáramú áramkörökhöz

- Teljesítménykompenzációs kondenzátorok

- Nagyfeszültségű kondenzátorok

- Kondenzátorok indukciós fűtéshez

- Impulzuskondenzátorok

- DC LINK kondenzátorok

- Kondenzátorok AC/DC áramkörökhöz

- Przejdź do podkategorii

- Interferencia szűrők

- Szuperkondenzátorok

- Túlfeszültség elleni védelem

- TEMPEST Felfedő emissziós szűrők

- Przejdź do podkategorii

-

Relék és kontaktorok

- Relék és kontaktorok elmélete

- AC háromfázisú félvezető relék

- DC szilárdtest relék

- Szabályozók, vezérlőrendszerek és tartozékok

- Lágyindítás és irányváltó kontaktorok

- Elektromechanikus relék

- Kontaktorok

- Forgókapcsolók

-

Egyfázisú AC szilárdtest relék

- Egyfázisú váltakozó áramú szilárdtestrelék, 1. sorozat | D2425 | D2450

- Egyfázisú AC szilárdtest relék CWA és CWD sorozat

- Egyfázisú AC szilárdtest relék CMRA és CMRD sorozat

- Egyfázisú AC félvezető relék PS sorozat

- AC szilárdtest relék kettős és négyes sorozatú D24 D, TD24 Q, H12D48 D

- GN sorozatú egyfázisú szilárdtest relék

- Egyfázisú AC szilárdtest relék CKR sorozat

- Egyfázisú AC DIN sínes relék ERDA és ERAA SERIES

- Egyfázisú váltakozó áramú relék 150A áramerősséghez

- Kettős szilárdtest relék DIN sínes hűtőbordával integrálva

- Przejdź do podkategorii

- AC egyfázisú nyomtatható félvezető relék

- Interfész relék

- Przejdź do podkategorii

- Magok és egyéb induktív alkatrészek

- Radiátorok, Varisztorok, Hővédelem

- Rajongók

- Klíma, Kapcsolószekrény tartozékok, Hűtők

-

Akkumulátorok, töltők, puffer tápegységek és átalakítók

- Akkumulátorok, töltők - elméleti leírás

- Lítium-ion akkumulátorok. Egyedi akkumulátorok. Akkumulátorkezelő rendszer (BMS)

- Elemek

- Akkumulátortöltők és tartozékok

- UPS és puffer tápegységek

- Átalakítók és tartozékok napelemekhez

- Energiatárolás

- Hidrogén üzemanyagcellák

- Lítium-ion cellák

- Przejdź do podkategorii

- Automatizálás

-

Kábelek, Litz vezetékek, vezetékek, rugalmas csatlakozások

- Vezetékek

- Kábeltömszelencék és -hüvelyek

- Arcok

-

Kábelek speciális alkalmazásokhoz

- Hosszabbító és kiegyenlítő kábelek

- Hőelem kábelek

- Csatlakozó kábelek PT érzékelőkhöz

- Többeres kábelek hőm. -60°C és +1400°C között

- SILICOUL középfeszültségű kábelek

- Gyújtókábelek

- Fűtőkábelek

- Egyeres kábelek hőm. -60°C és +450°C között

- Vasúti vezetékek

- Fűtőkábelek pl

- Kábelek a védelmi ipar számára

- Przejdź do podkategorii

- pólók

-

Zsinór

- Lapos zsinór

- Kerek fonatok

- Nagyon rugalmas fonat - lapos

- Nagyon rugalmas zsinór - kerek

- Hengeres rézfonatok

- Réz hengeres fonatok és borítások

- Rugalmas földelő hevederek

- Horganyzott és rozsdamentes acélból készült hengeres fonatok

- PVC szigetelt rézfonatok - 85 fokos hőmérsékletig

- Lapos alumínium fonatok

- Csatlakozókészlet - zsinórok és csövek

- Przejdź do podkategorii

- Vontatási berendezések

- Kábelsaruk

- Szigetelt rugalmas sínek

- Többrétegű rugalmas sínek

- Kábelkezelő rendszerek

- Przejdź do podkategorii

- Az összes kategória megtekintése

-

Félvezetők

-

-

- Szállítók

-

Alkalmazások

- Bányászat, kohászat és öntöde

- Berendezések elosztó- és kapcsolószekrényekhez

- CNC gépek

- DC és AC hajtások (inverterek)

- Energetika

- Energia bankok

- Faszárító és -feldolgozó gépek

- Gépek műanyagok hőformázásához

- Hegesztőgépek és hegesztők

- Hőmérséklet mérés és szabályozás

- HVAC automatizálás

- Indukciós fűtés

- Ipari automatizálás

- Ipari védőfelszerelés

- Kutatási és laboratóriumi mérések

- Motorok és transzformátorok

- Nyomtatás

- Robbanásveszélyes zónák alkatrészei (EX)

- Tápegységek (UPS) és egyenirányító rendszerek

- Villamos és vasúti vontatás

-

Telepítés

-

-

Induktorok

-

-

Indukciós eszközök

-

-

https://www.dacpol.eu/pl/naprawy-i-modernizacje

-

-

Szolgáltatás

-

- Kapcsolat

- Zobacz wszystkie kategorie

Zaawansowany projekt układu scalonego Si-IGBT dla maksymalnej wydajności całego systemu

Zaawansowany projekt układu scalonego Si-IGBT dla maksymalnej wydajności całego systemu

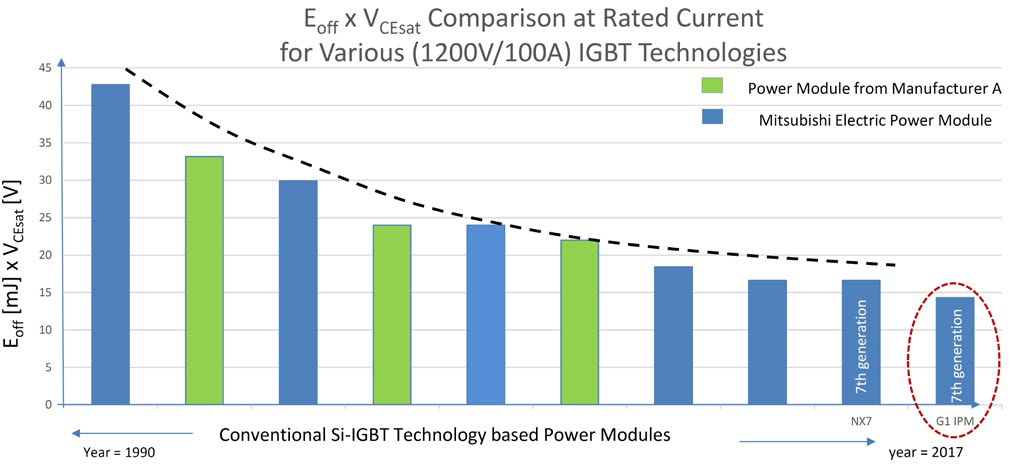

Ogólna wydajność systemu jest bez wątpienia w znacznym stopniu uzależniona od wyboru zastosowanej technologii półprzewodnikowej. W przypadku konwencjonalnych modułów IGBT, niedawne postępy w zakresie stosunku VCEsat do Eoff pokazują tendencję do nasycenia, co oznacza, że poprawki wydajności w kolejnych generacjach układów IGBT nie wskazują już na znaczący krok w poprawie efektywności. Dzięki nowej serii układów G1-IPM możliwe jest uzyskanie znacznej poprawy efektywności systemu poprzez zastosowanie zaawansowanego układu Si-IGBT i wprowadzenie adaptacyjnego sterowania bramkowego.

Autorzy: Narender Lakshmanan i Thomas Radke, Mitsubishi Electric Europe B.V.

Wstęp:

Mitsubishi Electric wprowadził na rynek nową serię inteligentnych modułów mocy (IPM) G1 z zaawansowanym układem Si-IGBT, aby rozwiązać kilka kluczowych parametrów wydajnościowych i umożliwić użytkownikowi końcowemu osiągnięcie wysokiej wydajności systemu. Postępy w technologii chipów G1 IPM mają na celu rozwiązanie niektórych wrodzonych wad Si-IGBT, zwłaszcza w przypadku zastosowań sterowania silnikiem. Układ G1 IPM został opracowany poprzez wdrożenie kilku kluczowych innowacji w najnowszej 7. generacji układu IGBT. Można zauważyć (patrz Rysunek 1), że w porównaniu do konwencjonalnego układu Si-IGBT 7. generacji, zaawansowana technologia chipu G1 IPM oferuje znaczne korzyści, chociaż należy do tej samej generacji chipów.

Rysunek 1: Porównanie wskaźnika VCEsat x EOFF dla różnych technologii Si-IGBT

Zdolność do zwarcia i wydajność elektryczna:

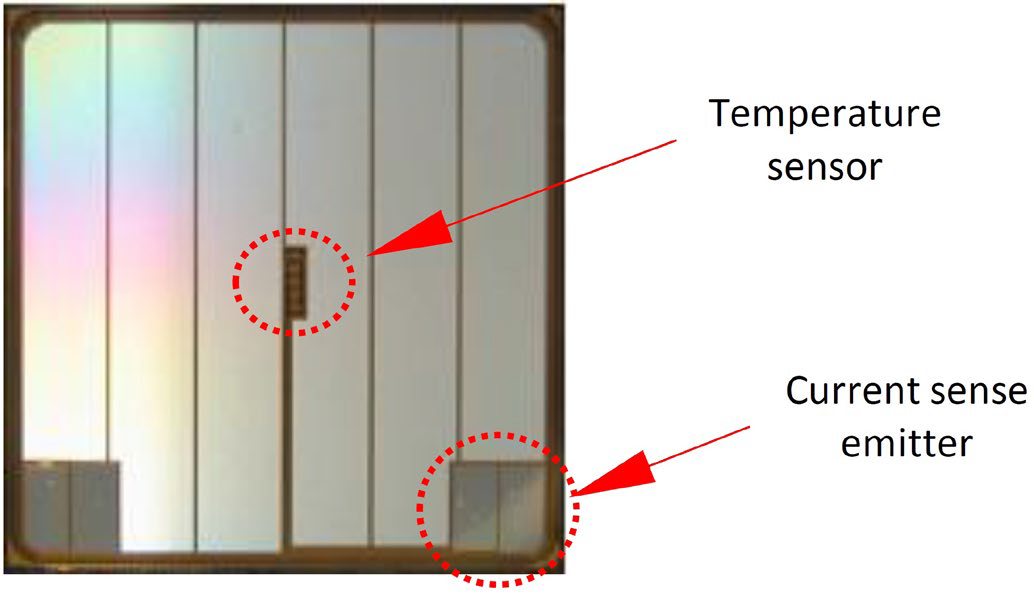

Ochrona przed zwarciem dla konwencjonalnego układu Si-IGBT została zaimplementowana za pomocą systemu opartego na „wykrywaniu desaturacji”, w którym obserwuje się napięcie VCE na IGBT w celu potwierdzenia wystąpienia zwarcia. Aby umożliwić skuteczne wykrycie, konwencjonalne układy Si-IGBT są projektowane w taki sposób, że wiele komórek bramkowych w chipie pozostaje niepodłączonych [6][2]. Chociaż zapewnia to, że IGBT wchodzi w tryb desaturacji powyżej określonej wartości IC, oznacza to również, że kilka parametrów elektrycznych jest pewnym stopniu kompromisowych [6][2][3]. Układ G1 IPM posiada chip Si-IGBT z monolitycznie zintegrowanym emiterem prądu (patrz Rysunek 2). Cechą emitera prądu jest umożliwienie oceny prądu kolektora IGBT poprzez bezpośrednie pomiar. Na podstawie informacji z emitera prądu można przypisać poziomy przerwy i rozpocząć wyłączanie SC przed desaturacją chipu. To podejście do bezpośredniego określania chwilowego IC czyni system oparty na wykrywaniu desaturacji na podstawie VCE przestarzałym. Nie jest już konieczne zapewnienie, że IGBT przechodzi w tryb desaturacji. Bezpośrednim skutkiem tego jest to, że wszystkie dostępne komórki bramkowe w chipie Si-IGBT mogą być połączone, co przekształca chip w „pełny IGBT” i pozwala na wykorzystanie korzyści elektrycznych wynikających z większego wykorzystania chipa Si-IGBT [1]. Ponadto, chip IGBT jest wyposażony w diodę czujnika temperatury na chipie, umieszczoną centralnie na chipie, w celu skutecznego określenia temperatury złącza IGBT (patrz Rysunek 2).

Rysunek 2: Czujnik temperatury i komponent emitera prądu na chipie IGBT w G1-IPM

Szybkość zmiany napięcia (dv/dt) jako czynnik ograniczający wydajność:

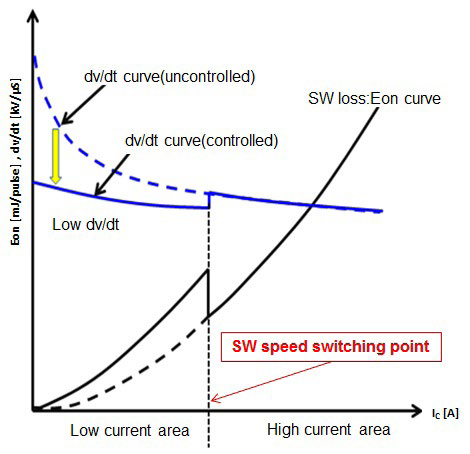

Jednym z czynników negatywnie wpływających na żywotność warstw izolacyjnych w systemie (izolacja uzwojenia silnika lub izolacja kabla) jest ekspozycja na wysokie prędkości przejściowe napięć (dv/dt). Zdarzenie przełączania IGBT jest zdolne do generowania wysokiego dv/dt na zaciskach modułu mocy (szczególnie podczas zdarzenia włączania). Konwencjonalnym rozwiązaniem tego problemu jest ograniczenie prędkości przełączania IGBT poprzez zastosowanie impedancji bramkowej tak, aby dv/dt przełączania było utrzymywane poniżej określonego poziomu. Charakterystyka dv/dt vs IC jest taka, że najwyższe dv/dt (najgorszy przypadek dv/dt) występuje podczas włączania przy niskim IC, a dv/dt włączania zmniejsza się wraz ze wzrostem IC. Chociaż najgorszy przypadek dv/dt generowany jest tylko podczas włączania przy niskim IC, konwencjonalny sterownik bramkowy z ustalonymi rezystorami włączania bramki wymusi ograniczenie prędkości przełączania dla wszystkich wartości IC. Takie podejście generuje znaczne straty włączania przy pracy przy wysokim IC, nawet jeśli dv/dt przełączania nie jest najgorszym przypadkiem podczas pracy przy wysokim IC. Jasne jest więc, że dla konwencjonalnej technologii Si-IGBT istnieje kompromis między kontrolą najgorszego przypadku dv/dt a wydajnością.

Rysunek 3: Wykorzystanie emitera prądu do implementacji kontroli prędkości przełączania w G1 IPM

Wykorzystanie emitera prądu do kontroli dv/dt bez uszczerbku dla wydajności:

Dostęp do emitera prądu w zaawansowanym układzie Si-IGBT otwiera możliwość określenia IC. Na podstawie zależności dv/dt vs IC wynika, że w celu skierowania najgorszego przypadku dv/dt, odpowiednie jest wprowadzenie ograniczenia prędkości przełączania tylko podczas przełączania przy niskim IC. Zgodnie z tym kluczowym punktem, w układach G1 IPM Si-IGBT zastosowano technikę przełączania, w której prędkość przełączania włączania jest regulowana na podstawie IC. Jeśli IC (na podstawie danych z emitera prądu) zostanie ustalone jako niższe niż określony próg, jednostka napędu bramki zostanie poinformowana o zastosowaniu ograniczenia prędkości przełączania, aby uniknąć najgorszego przypadku dv/dt. Gdy prąd IC przekroczy predefiniowaną wartość progową, jednostka napędu bramki zostanie poinformowana o włączeniu IGBT z wyższą prędkością przełączania, tak aby można było zoptymalizować straty włączania. Dzięki temu podejściu unika się najgorszego przypadku dv/dt podczas przełączania, jednocześnie zapewniając, że efektywność systemu nie jest kompromitowana (patrz Rysunek 3).

Pełny IGBT z emiterem prądu - Analiza ogólnej wydajności:

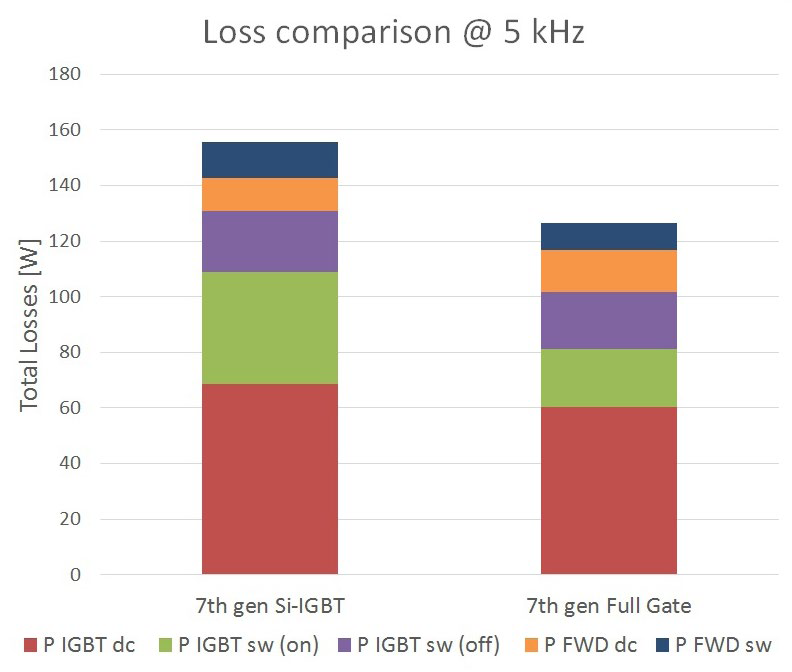

Moduł G1 IPM wykorzystuje pełny IGBT 7. generacji wyposażony w monolitycznie zintegrowany emiter prądu. To podejście ma na celu połączenie korzyści płynących z pełnego IGBT wraz z zaletami komponentu emitera prądu. Celem jest zapewnienie maksymalnej wydajności, wysokiej niezawodności (ochrona SC oparta na chwilowym prądzie IC) i akceptowalnego profilu EMI (kontrola dv/dt). Rysunek 4 przedstawia porównanie całkowitej straty mocy całkowitej układu dla pełnego bramkowego układu 7. generacji z konwencjonalnym układem Si-IGBT (przy tej samej wartości dv/dt podczas włączania). Jak wynika z Ryciny 4, układ pełnego IGBT generuje około 18% mniejsze straty ogólne niż układ konwencjonalny podczas wymienionych warunków pracy.

Rysunek 4: Porównanie całkowitej straty mocy generowanej przez pojedyncze połączenie IGBT + dioda w układzie pełnej bramki 7. generacji (100A/1200V) i 7. generacji Si-IGBT (100A/1200V) dla warunków: VCC = 600V, Iout = 100 A rms, fC = 5 kHz, m = 1, cos(φ) = 0,8, TS = 80°C, fo = 50 Hz

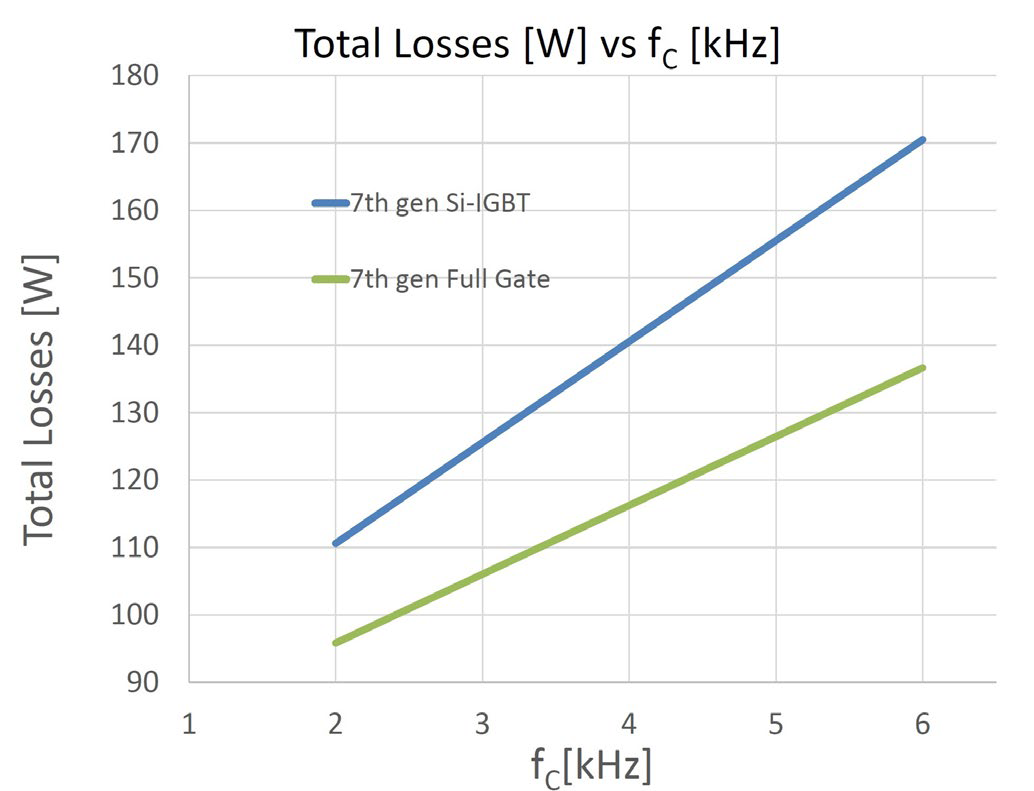

Rysunek 5: Porównanie całkowitych strat generowanych w pojedynczym połączeniu IGBT + dioda w układzie pełnej bramki 7. generacji (100A/1200V) i 7. generacji Si-IGBT (100A/1200V) dla kilku częstotliwości przełączania. Warunki: VCC = 600V, Iout = 100 Arms, m = 1, cos (φ) = 0,8, Ts = 80°C, fo = 50 Hz

W warunkach wymienionych na Rysunku 4, technika kontroli prędkości przełączania pozwala na redukcję strat włączania o 48%. Pełne IGBT (z emiterem prądu) wyraźnie generuje znacznie mniejsze straty przełączania w porównaniu do swojego konwencjonalnego odpowiednika. Rysunek 5 przedstawia całkowitą stratę mocy w zależności od fC (częstotliwość przełączania) dla pełnego IGBT (z emiterem prądu) i układu konwencjonalnego Si-IGBT. Różnica w wydajności między pełnym IGBT (z emiterem prądu) a konwencjonalnym Si-IGBT wzrasta wraz ze wzrostem fC.

Dla aplikacji, które wymagają pracy przy niskim poziomie hałasu słyszalnego (wymagane są wysokie częstotliwości przełączania), 7. generacja pełnego IGBT (z emiterem prądu) obiecuje ogromne korzyści na poziomie systemu. Istnieją pewne punkty przeciążenia dla aplikacji sterowania silnikiem. Podczas bezruchu (silnik zablokowany) - prąd obciążenia nie jest równomiernie rozłożony między IGBT w falowniku, a podczas bardzo niskich częstotliwości wyjściowych - IGBT w falowniku mogą doświadczyć wysokiej pulsacji prądu. W takich warunkach przeciążenia istotne jest określenie temperatur złączy IGBT każdego chipa, aby uniknąć awarii związanej z przegrzaniem. Temperaturę złącza IGBT można skutecznie monitorować za pomocą wbudowanego czujnika temperatury na każdym chipie.

Można zatem stwierdzić, że pełny IGBT wyposażony w emiter prądu i czujnik temperatury rozwiązuje kilka kluczowych problemów związanych z konwencjonalnym podejściem Si-IGBT, co pozwala deweloperowi falownika osiągnąć znacznie wyższą wydajność systemu.

Źródła:

[1] An Advanced Si-IGBT Chip for Delivering Maximum Overall System Performance, Narender Lakshmanan i Thomas Radke, Proc. PCIM 2017

[2] USING F-SERIES IGBT MODULES, MITSUBISHI ELECTRIC. Nota aplikacyjna. Luty 2000

[3] New chip design technology for next generation power module. Katsumi Satoh i inni, Proc. PCIM 2008

[4] A 6-in-1 IGBT module performance evaluation platform determining the trade-off between dV/dt and turn-on loss of different IGBT/FwDi chip setups, Marco Honsberg i inni, Proc. EPE 2011

[5] Karta danych - CM100TX-24T

[6] A Novel Series of Intelligent Power Modules “V1” with Internally Paralleled FULL GATE CSTBTTM and mirror Emitter technology for short circuit sensing, Nishida Nobuya i inni, Proc. PCIM 2010

Related posts

Nowości w dziale zasilacze, przetwornice i inwertery – inwertery Premium

Nowości w dziale zasilacze, przetwornice i inwertery – inwertery Premium

Oświetlenie do obrabiarek– oprawy KIRA!

Oświetlenie do obrabiarek– oprawy KIRA!

Leave a comment