-

вернутьсяX

-

Компоненты

-

-

Category

-

Полупроводниковые приборы

- Диоды

- Тиристоры

-

Электро-изолированные модули

- Электроизолированные модули | ВИШАЙ (ИК)

- Электроизолированные модули | INFINEON (EUPEC)

- Электроизолированные модули | Семикрон

- Электроизолированные модули | POWEREX

- Электроизолированные модули | IXYS

- Электроизолированные модули | ПОЗЕЙКО

- Электроизолированные модули | ABB

- Электроизолированные модули | TECHSEM

- Перейти в подкатегорию

- Выпрямительные мостики

-

Транзисторы

- Транзисторы | GeneSiC

- Модули SiC MOSFET | Mitsubishi

- Модули SiC MOSFET | STARPOWER

- Модули ABB SiC MOSFET

- Модули IGBT | МИЦУБИСИ

- Транзисторные модули | MITSUBISHI

- Модули MOSFET | МИЦУБИСИ

- Транзисторные модули | ABB

- Модули IGBT | POWEREX

- Модули IGBT | INFINEON (EUPEC)

- Полупроводниковые элементы из карбида кремния (SiC)

- Перейти в подкатегорию

- Драйвера

- Блоки мощности

- Перейти в подкатегорию

- Электрические преобразователи

-

Пассивные компоненты (конденсаторы, резисторы, предохранители, фильтры)

- Резисторы

-

Предохранители

- Миниатюрные предохранители для электронных плат серии ABC и AGC

- Быстрые трубчатые предохранители

- Медленные вставки с характеристиками GL/GG и AM

- Ультрабыстрые плавкие вставки

- Быстрые предохранители английский и американский стандарт

- Быстрые предохранители европейский стандарт

- Тяговые предохранители

- Высоковольтные предохранительные вставки

- Перейти в подкатегорию

-

Конденсаторы

- Конденсаторы для электромоторов

- Электролитические конденсаторы

- Конденсаторы типа snubbers

- Конденсаторы мощности

- Конденсаторы для цепей DC

- Конденсаторы для компенсации пассивной мощности

- Высоковольтные конденсаторы

- Конденсаторы большой мощности для индукционного нагрева

- Импульсные конденсаторы

- Конденсаторы звена постоянного тока

- Конденсаторы для цепей переменного/постоянного тока

- Перейти в подкатегорию

- Противопомеховые фильтры

- Ионисторы

-

Защита от перенапряжения

- Ограничители перенапряжения для приложений RF

- Ограничители перенапряжения для систем технического зрения

- Ограничители перенапряжения для линий электропередач

- Ограничители перенапряжения для светодиодов

- Ограничители перенапряжения для фотовольтаики

- Ограничители перенапряжения для систем взвешивания

- Ограничители перенапряжения для Fieldbus

- Перейти в подкатегорию

- Перейти в подкатегорию

-

Реле и контакторы

- Теория реле и контакторы

- Полупроводниковые реле AC 3-фазные

- Полупроводниковые реле DC

- Контроллеры, системы управления и аксессуары

- Системы плавного пуска и реверсивные контакторы

- Электро-механические реле

- Контакторы

- Оборотные переключатели

-

Полупроводниковые реле AC 1-фазные

- РЕЛЕ AC 1-ФАЗНЫЕ СЕРИИ 1 D2425 | D2450

- Однофазное реле AC серии CWA и CWD

- Однофазное реле AC серии CMRA и CMRD

- Однофазное реле AC серии PS

- Реле AC двойное и четверное серии D24 D, TD24 Q, H12D48 D

- Однофазные твердотельные реле серии gn

- Однофазные полупроводниковые реле переменного тока серии ckr

- Однофазные реле переменного тока ERDA И ERAA SERIES для DIN-рейки

- Однофазные реле переменного тока на ток 150А

- Двойные твердотельные реле, интегрированные с радиатором для DIN-рейки

- Перейти в подкатегорию

- Полупроводниковые реле AC 1-фазные для печати

- Интерфейсные реле

- Перейти в подкатегорию

- Индукционные компоненты

- Радиаторы, варисторы, термическая защита

- Вентиляторы

- Кондиционеры, оборудование для шкафов, охладители

-

Аккумуляторы, зарядные устройства, буферные источники питания и инверторы

- Аккумуляторы, зарядные устройства - теоретическое описание

- Модульные литий-ионные аккумуляторы, пользовательские батареи, Система управления батареями (BMS)

- Аккумуляторы

- Зарядные устройства и аксессуары

- Резервный источник питания ИБП и буферные источники питания

- Преобразователи и аксессуары для фотовольтаики

- Хранилище энергии

- Топливные элементы

- Литий-ионные аккумуляторы

- Перейти в подкатегорию

-

Автоматика

- Futaba Drone Parts

- Концевые выключатели, Микровыключатели

- Датчики Преобразователи

- Пирометры

- Счетчики, Реле времени, Панельные измерительные приборы

- Промышленные защитные устройства

- Световые и звуковые сигнальные установки

- Термокамеры, Тепловизоры

- LED-экраны

- Управляющая аппаратура

-

Регистраторы

- Регистраторы температуры с записью на ленту и с цифровым показателем - AL3000ym - AL3000

- Микропроцесорные регистраторы с экраном LCD серия KR2000

- Регистратор KR5000

- Измеритель с функцией регистрации влажности и температуры HN-CH

- Эксплуатационные материалы для регистраторов

- Компактный графический регистратор 71VR1

- Регистратор KR 3000

- Регистратор PC серии R1M

- Регистратор PC серии R2M

- Регистратор PC, USB, 12 изолированных входов – RZMS

- Регистратор PC, USB, 12 изолированных входов – RZUS

- Перейти в подкатегорию

- Перейти в подкатегорию

-

Провода, литцендрат, гофрированные рукава, гибкие соединения

- Провода

- Многожильные провода (Lica)

-

Кабели и провода для специальных применений

- Удлинительные и компенсационные провода

- Провода для термопар

- Присоединительные провода для датчиков PT

- Многожильные провода темп. от -60C до +1400C

- Провода среднего напряжения

- Провода зажигания

- Нагревательные провода

- Одножильные провода темп. от -60C до +450C

- Железнодородные провода

- Нагревательные провода в Ex

- Перейти в подкатегорию

- Оболочки

-

Плетеные кабели

- Плоские плетеные кабели

- Круглые плетеные кабели

- Очень гибкие плетеные кабели - плоские

- Очень гибкие плетеные кабели - круглые

- Медные цилиндрические плетеные кабели

- Медные цилиндрические плетеные кабели и кожуха

- Гибкие заземляющие ленты

- Цилиндрические плетеные провода из луженой и нержавеющей стали

- Медные изолированные плетеные провода PCV - температура до 85 градусов C

- Плоские алюминиевые плетеные провода

- Соединительный набор - плетеные провода и трубки

- Перейти в подкатегорию

- Аксессуары для тяги

- Кабельные наконечники

- Изолированные эластичные шины

- Многослойные гибкие шины

- Системы прокладки кабеля (PESZLE)

- Трубы

- Перейти в подкатегорию

- Просмотреть все категории

-

Полупроводниковые приборы

-

-

- Поставщики

-

Программы

- Energy bank

- Автоматика HVAC

- Горное дело, металлургия и литейное дело

- Двигатели и трансформаторы

- Измерение и регулирование температуры

- Измерение и регулирование температуры

- Индукционный нагрев

- Индустриальная автоматизация

- Источники питания (ИБП) и выпрямительные системы

- Компоненты для потенциально взрывоопасных сред (EX)

- Машины для сушки и обработки древесины

- Машины для термоформования пластмасс

- Оборудование для распределительных, контрольных и телекоммуникационных шкафов

- Печать

- Приводы переменного и постоянного тока (инверторы)

- Промышленная автоматика

- Промышленные защитные устройства

- Сварочные аппараты и сварочные аппараты

- Станки с ЧПУ

- Трамвай и ж / д тяга

-

Монтаж

-

-

Индукторы

-

-

Индукционные устройства

-

-

https://www.dacpol.eu/pl/naprawy-i-modernizacje

-

-

Услуга

-

- Контакт

- Zobacz wszystkie kategorie

Advanced Si-IGBT Chip Design for Maximum Overall System Performance

Advanced Si-IGBT Chip Design for Maximum Overall System Performance

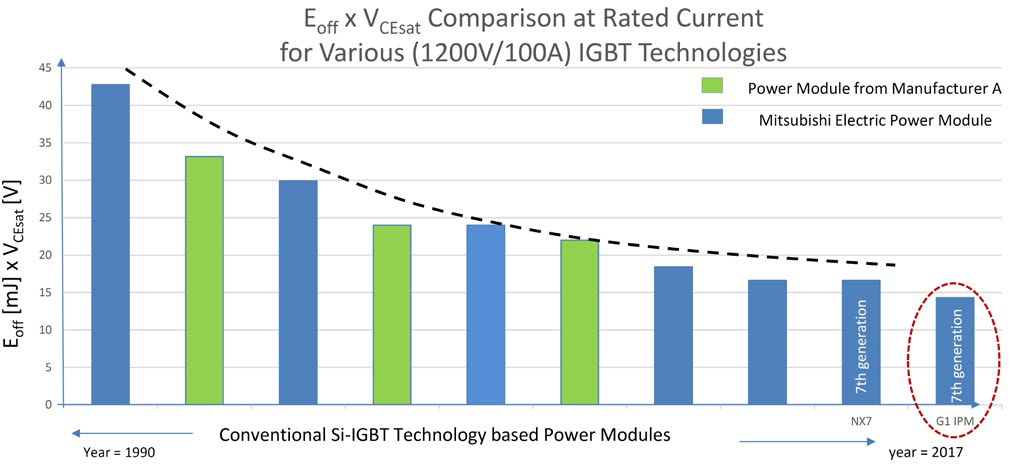

The overall system performance is undoubtedly influenced to a significant extent by the choice of the power semiconductor technology employed. For conventional IGBT modules, the recent improvements in the VCEsat vs. Eoff trade-off shows a tendency towards saturation and hence the performance improvement of upcoming IGBT chip generations do not indicate a significant step in efficiency improvements anymore. With the new G1- IPM series it is possible to obtain substantial system efficiency improvement by utilizing an advanced Si-IGBT chip and implementing an adaptive gate control.

By Narender Lakshmanan and Thomas Radke, Mitsubishi Electric Europe B.V.

Introduction:

Mitsubishi Electric has introduced the new G1 series Intelligent Power Modules (IPM) with an advanced Si-IGBT design to address several key performance parameters and enable the end-user to achieve high system performance. The advancements in the G1 IPM chip technology are aimed at resolving some inherent drawback of the Si-IGBT especially when it is employed for motor control applications. The G1 IPM device has been developed by implementing some key advancements in the latest 7th generation IGBT. It can be noticed (refer Figure 1) that in comparison to the 7th generation conventional Si-IGBT, the advanced G1 IPM chip technology offers significant benefits although it belongs to the same chip generation.

Figure 1 : A comparison of the VCEsat x EOFF index for different Si-IGBT technologies

Short Circuit Capability and Electrical Performance:

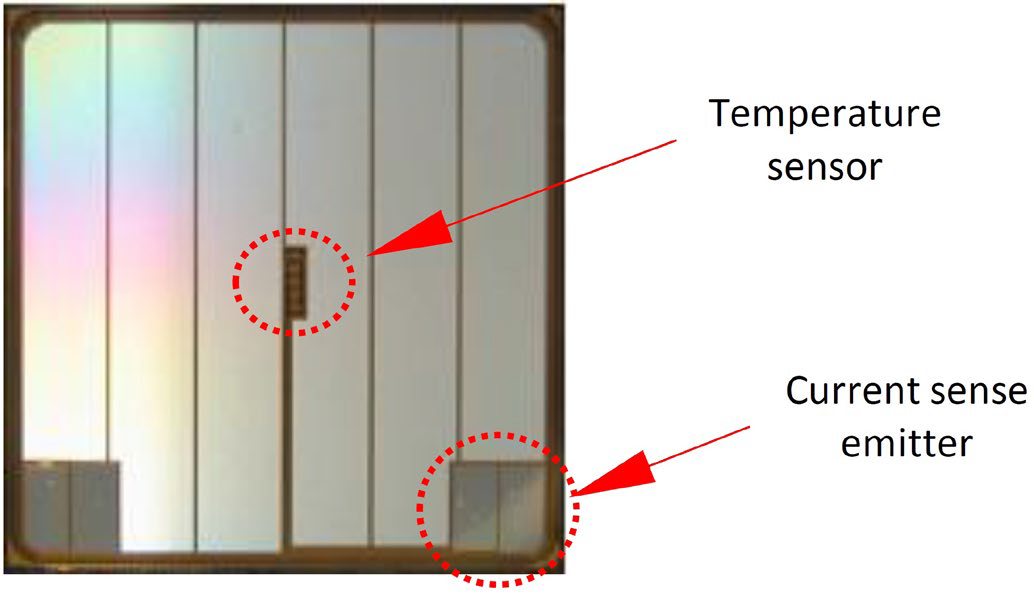

Short circuit protection for a conventional Si-IGBT has been implemented using a ‘desaturation detection’ based system where the VCE across the IGBT is observed to ascertain the occurrence of a short circuit event. To facilitate a successful detection, the conventional Si-IGBT devices are designed such that several gate cells in the chip are left unconnected [6][2]. While this ensures that the IGBT enters into the desaturation mode beyond a particular value of IC, it also means that several electrical parameters are compromised to a certain extent [6][2][3]. The G1 IPM possess a Si-IGBT chip with a monolithically integrated current sense emitter (refer figure 2). The sense emitter feature facilitates an assessment of the IGBT collector current via direct measurement. Based on the input from the sense emitter, trip levels can be assigned and an SC turn-off can be initiated before the chip desaturates. This approach to directly determine the instantaneous IC renders the VCE based desaturation detection system obsolete. Thus, it is no longer necessary to ensure that the IGBT enters into the desaturation mode. As a direct consequence, all available gate cells in the Si-IGBT chip can be connected transforming the chip into a ‘full gate IGBT’ and the subsequent electrical benefits can be harvested due to the enhanced utilization of the Si-IGBT chip [1]. Additionally, the IGBT chip is provided with an on-chip temperature sensing diode in the center of the chip in order to ascertain the IGBT junction temperature with maximum effectiveness (refer figure 2).

Figure 2 : The temperature sensor and the current sense emitter components of the IGBT chip in the G1-IPM

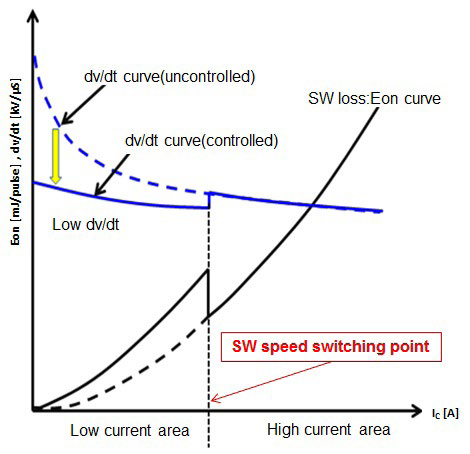

Switching dv/dt as a Performance Limiting Factor:

One factor that negatively influences the lifetime of the insulation layers in the system (motor winding insulation or cable insulation) is the exposure to high speed transient voltages (dv/dt). The IGBT switching event is capable of generating high dv/dt at the terminals of the power module (especially during a turn-on event). A conventional solution to address this issue is to restrict the switching speed of the IGBT by employing a gate impedance such that the switching dv/dt is maintained below a particular level. The dv/dt versus IC characteristics is such that the highest dv/dt (worst case dv/dt) is experienced during turn-on of low IC and the turn-on dv/dt reduces with an increase in IC. Although the worst case dv/dt would be generated only during turn-on of low IC, a conventional gate driver with fixed turn-on gate resistances will force a restriction of switching speed for all values of IC. This approach will generate significant turn-on losses while operating at high IC even though the switching dv/dt is not the worst case during high IC operation. It is therefore clear that for conventional Si-IGBT technology, there is a trade-off between controlling the worst-case dv/ dt and efficiency.

Figure 3 : Utilization of the sense emitter to implement a switching speed control in the G1 IPM

Utilizing Sense Emitter to Control dv/dt Without Sacrificing Efficiency:

The sense emitter provision in the advanced full gate Si-IGBT open up the possibility to ascertain the IC. Based on the dv/dt vs IC dependency, it is clear that to address the worst case dv/dt, it is appropriate to implement a switching speed restriction only during the switching of low IC. Considering this key point, a switching technique has been implement in the G1 IPM Si-IGBT devices where the turn-on switching speed in regulated based on the IC. If the IC (from the sense emitter data) is ascertained to be below a particular threshold, the gate drive unit will be informed to apply a switching speed restriction such that the worst case dv/dt is avoided. When the switching IC exceeds the pre-set threshold value, the gate drive unit will be informed to turn the IGBT ON with a higher switching speed, such that the turn-on losses can be optimized. With this approach, the worst case dv/dt is avoided during switching, while simultaneously ensuring that the system efficiency is not compromised (refer Figure 3).

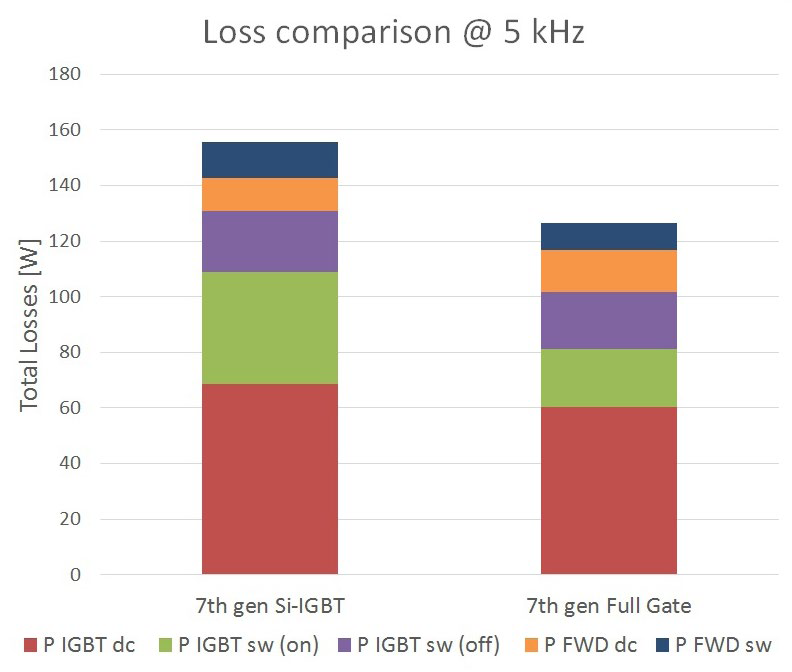

Full Gate IGBT with Sense Emitter - Analysis of Overall Performance:

The G1 IPM module utilizes the full gate 7th generation Si-IGBT which is equipped with the monolithically integrated sense emitter. This approach is aimed at combining the benefits of the full gate Si-IGBT along with the advantages of the sense emitter component. The target is to ensure maximum efficiency, high reliability (instantaneous IC based SC protection) and an acceptable EMI profile (dv/dt control). Figure 4 shows a comparison of the overall power loss performance of the full gate device with the conventional Si-IGBT (under same turn-on dv/dt condition). As evident from Figure 4, the full gate IGBT device generates approximately 18% less overall losses than the conventional Si-IGBT device under the mentioned working conditions.

Figure 4 : The comparison of the total power loss generated by a single IGBT + Diode combination in the 100A/1200V 7th gen Full Gate device and the 7th gen Si-IGBT (100A/1200V) for the conditions: VCC = 600V, Iout = 100 A rms, fC = 5 kHz, m = 1, cos(φ) = 0.8, TS = 80°C, fo = 50 Hz

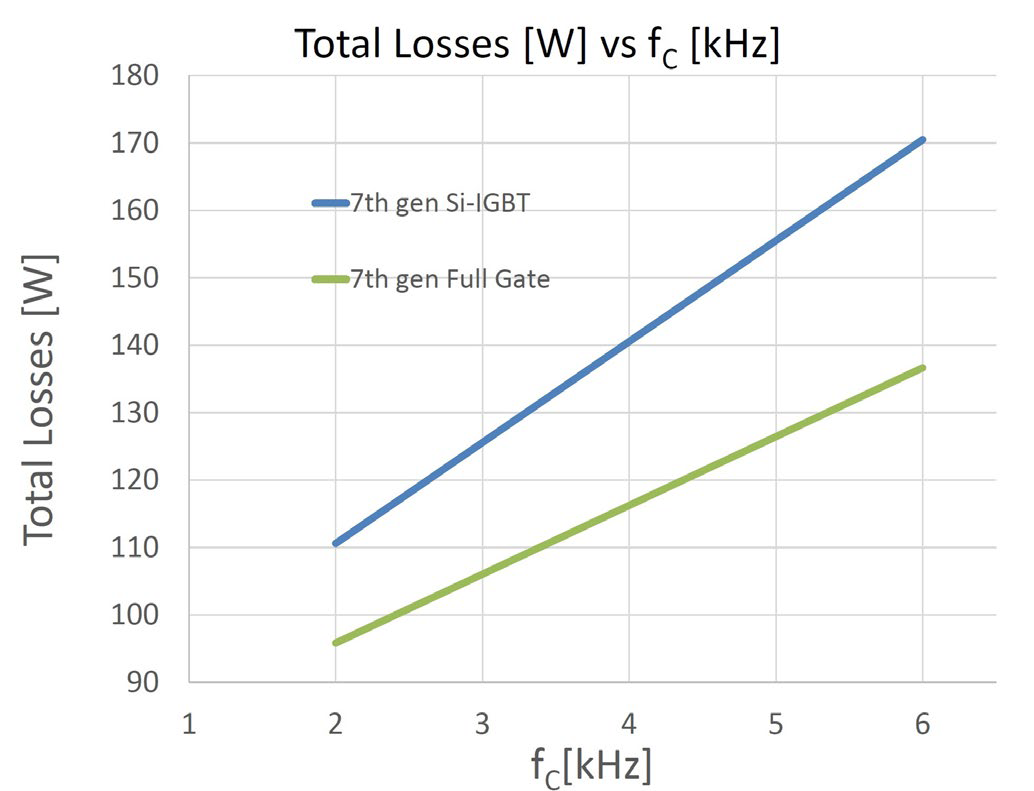

Figure 5: The Comparison of total losses generated in a single IGBT + Diode combination in the 100A/1200V 7th gen Full Gate device and the 7th gen Si-IGBT (100A/1200V) for several switching frequencies. Conditions: VCC= 600V, Iout = 100 Arms, m = 1, cos (φ) = 0.8, Ts = 80°C, fo = 50 Hz

Under the conditions mentioned in Figure 4, the switching speed control technique allows for a 48% reduction in the turn-on losses. The full gate IGBT (with sense emitter) clearly generates significantly lower switching loss versus its convention counterpart. Figure 5 shows the overall power loss versus fC (switching frequency) of the full gate (with sense emitter) IGBT and the conventional Si-IGBT device. The gap in performance between the full gate IGBT (with sense emitter) and the conventional Si-IGBT increases with an increase in the fC.

For applications which require an operation at low levels of audible noise (high switching frequencies are necessary), the 7th generation full gate IGBT (with sense emitter) promises enormous system level benefits. Certain overload operation points exist for motor control applications. During the stand-still (locked rotor) condition - the load current is not symmetrically distributed among the inverter IGBTs, and during extremely low output frequencies - the inverter IGBTs can experience a high current ripple. Under such overload conditions, it is crucial to determine the IGBT junction temperatures of each chip to avoid an over-temperature failure event. The IGBT junction temperature can be effectively monitored using the on-chip temperature sensor integrated on each chip.

It can thus be concluded that the full gate Si-IGBT equipped with the sense emitter feature and the on-chip temperature sensor address several key challenges which were inherent to the conventional Si- IGBT approach thereby allowing the inverter developer to achieve significantly higher system performance.

References:

[1] An Advanced Si-IGBT Chip for Delivering Maximum Overall System Performance, Narender Lakshmanan and Thomas Radke, Proc. PCIM 2017

[2] USING F-SERIES IGBT MODULES, MITSUBISHI ELECTRIC. Application Note. Feb 2000

[3] New chip design technology for next generation power module. Katsumi Satoh et al., Proc. PCIM 2008

[4] A 6-in-1 IGBT module performance evaluation platform determining the trade-off between dV/dt and turn-on loss of different IGBT/ FwDi chip setups, Marco Honsberg, et al., Proc. EPE 2011

[5] Datasheet – CM100TX-24T

[6] A Novel Series of Intelligent Power Modules “V1” with Internally Paralleled FULL GATE CSTBTTM and mirror Emitter technology for short circuit sensing, Nishida Nobuya et al., Proc. PCIM 2010

Связанные посты

Now available – DC/DC converters from PREMIUM

Now available – DC/DC converters from PREMIUM

New release in DACPOL lighting for lathes – Kira covers

New release in DACPOL lighting for lathes – Kira covers

Оставить комментарий